# Diode-Like Selective Enhancement of Carrier Transport through a Metal-Semiconductor Interface Decorated by Monolayer Boron Nitride

Hemendra Nath Jaiswal, Maomao Liu, Simran Shahi, Sichen Wei, Jihea Lee, Anindita Chakravarty, Yutong Guo, Ruiqiang Wang, Jung Mu Lee, Chaoran Chang, Yu Fu, Ripudaman Dixit, Xiaochi Liu, Cheng Yang, Fei Yao,\* and Huamin Li\*

2D semiconductors such as monolayer molybdenum disulfide (MoS<sub>2</sub>) are promising material candidates for next-generation nanoelectronics. However, there are fundamental challenges related to their metalsemiconductor (MS) contacts, which limit the performance potential for practical device applications. In this work, 2D monolayer hexagonal boron nitride (h-BN) is exploited as an ultrathin decorating layer to form a metal-insulator-semiconductor (MIS) contact, and an innovative device architecture is designed as a platform to reveal a novel diode-like selective enhancement of the carrier transport through the MIS contact. The contact resistance is significantly reduced when the electrons are transported from the semiconductor to the metal, but is barely affected when the electrons are transported oppositely. A concept of carrier collection barrier is proposed to interpret this intriguing phenomenon as well as a negative Schottky barrier height obtained from temperature-dependent measurements, and the critical role of the collection barrier at the drain end is shown for the overall transistor performance.

H. N. Jaiswal, M. Liu, S. Shahi, A. Chakravarty, Y. Guo, R. Wang, J. M. Lee, R. Dixit, Prof. H. Li Department of Electrical Engineering University at Buffalo The State University of New York Buffalo, NY 14260, USA E-mail: huaminli@buffalo.edu S. Wei, J. Lee, C. Chang, Y. Fu, Prof. F. Yao Department of Materials Design and Innovation University at Buffalo The State University of New York Buffalo, NY 14260, USA E-mail: feiyao@buffalo.edu Prof. X. Liu School of Physics and Electronics Central South University Changsha 410083, China Prof. C. Yang School of Physics and Electronics **Shandong Normal University** Jinan 250014, China

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/adma.202002716.

DOI: 10.1002/adma.202002716

2D monolayer molybdenum disulfide (MoS<sub>2</sub>) as an n-type semiconducting transition metal dichalcogenides (TMDs) has been demonstrated as a promising material candidate for future energyefficient nanoelectronics[1-4] because of ultrathin body with enhanced electrostatic gating, natural carrier confinement, suitable bandgaps, passivated surfaces, good intrinsic carrier mobility, and mechanical flexibility.<sup>[5–11]</sup> To fully explore the potential of monolayer MoS2 for practical device and circuit applications, there is a critical need of metal-semiconductor (MS) contact engineering and optimization, which can lead to the maximization of device performance.[12-14] Especially for the extremely scaled short-channel devices, the contact condition between 2D semiconductors and 3D metals plays a more important role in the entire carrier transport process.<sup>[15,16]</sup> To lower Schottky barrier height (SBH) at the

MS interface and thus reduce contact resistance ( $R_c$ ), a variety of approaches for MoS<sub>2</sub>-based nanoelectronic devices have been proposed. On the 2D MoS<sub>2</sub> side, substitutional doping, [13] surface charge transfer doping, [17-20] isoelectronic alloying, [21-23] hybridization, [24] and phase engineering [25-26] can increase the carrier density of MoS<sub>2</sub> and thus reduce the contact barrier height. On the 3D metal side, although the effect of the conventional work function engineering following the Schottky–Mott rule is limited primarily due to the unique Fermi level pinning effect in MoS<sub>2</sub>, [27-29] it has been demonstrated that Al, [30] Sc, and Ti [31] contacts can provide the low SBHs for electrons, compared to MoO<sub>2</sub>, [32] graphene oxide (GO), [33] and NbS<sub>2</sub> [34] with the low SBHs for holes. Novel contact architecture such as 1D edge contact [35,36] and high-quality metal deposition condition such as ultrahigh vacuum [37] can also yield a low  $R_c$  value.

In addition to the engineering on 2D MoS<sub>2</sub> and 3D metals, contact decoration by introducing ultrathin foreign materials at the interface has been proposed as a new strategy to improve the MS contact. For example, graphene as an electrically active semimetal can form a 2D–2D MS contact with MoS<sub>2</sub>, and the gate-controlled Fermi level tunability of graphene can assist to reduce the SBHs.<sup>[38–41]</sup> As a comparison, the metal–insulator–semiconductor (MIS) contact has been proposed as well.

Various ultrathin insulators such as  ${\rm Ta_2O_5,^{[42]}\ TiO_2,^{[43,44]}}$  and MgO<sup>[45]</sup> have been demonstrated to reduce  $R_{\rm c}$ , introduce the Fermi level depinning effect, and consequently improve the device performance, primarily due to the reduction of the SBHs, the suppression of metal-induced gap states, and the formation of electric dipoles. As an atom-thick 2D layered insulator, hexagonal boron nitride (h-BN) with a bandgap of  $\approx$ 6 eV has been exploited in the MIS contact to depin the Fermi level and lower  $R_{\rm c}$ . [46–50] In principle, the insulating decoration layer in the MIS contact configuration should be thick enough to suppress the MS interfacial interaction, yet thin enough to provide a high tunneling probability for carrier transport through the insulator. As a result, there is a trade-off between the dominations of barrier height and tunneling resistance to obtain the lowest  $R_{\rm c}$ .

In this work, we designed an innovative platform where both the MS and MIS contacts can be achieved and compared on a single monolayer  $MoS_2$  triangle domain. First, we demonstrated the improved contact condition and consequently the boosted device performance of  $MoS_2$  field-effect transistors (FETs) by using the MIS contact decorated by a monolayer h-BN. Then, we discovered a novel diode-like selective enhancement of the carrier transport through the MIS contact, where the MIS contact can significantly reduce  $R_c$  and augment the electron transport from the semiconductor to the metal, but has negligible effects on the electron transport oppositely.

Finally, we exploited a concept of carrier collection barrier in a comparison with the conventional carrier injection barrier to understand the selective enhancement of the carrier transport through the MIS contact as well as a negative SBH obtained from temperature-dependent measurements, and showed the critical role of the collection barrier at the drain end for the overall transistor performance.

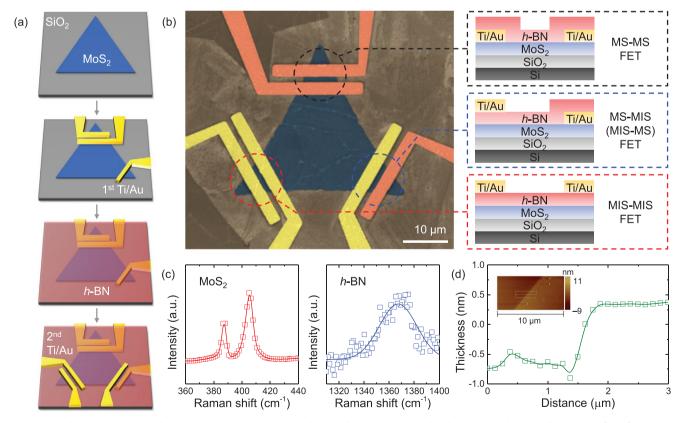

For a comparative study, we fabricate three types of globalback-gate transistor architectures and measure four different transistor configurations depending on the assignment of source and drain: an MS-source MS-drain (MS-MS) FET, an MIS-source MIS-drain (MIS-MIS) FET, an MS-source MISdrain (MS-MIS) FET, and an MIS-source MS-drain (MIS-MS) FET, as shown in Figure 1 and Figure S1 in the Supporting Information. The MS contact is made by a Ti/Au (10 nm/100 nm) layer and a monolayer MoS<sub>2</sub> (≈0.65 nm), and the MIS contact is made by adding a monolayer h-BN ( $\approx$ 0.4 nm)<sup>[51,52]</sup> between the Ti/Au layer and the monolayer  $MoS_2$ . Both  $MoS_2$  and h-BN are synthesized by chemical vapor deposition (CVD),[53,54] and their monolayer structures are confirmed by Raman spectroscopy and atomic force microscopy (AFM). Especially, we design and fabricate all three types of the device architectures on a monolayer MoS2 triangular domain with identical geometries including channel length and width (see the Experimental Section). Therefore, all the devices share the same quality of the MoS<sub>2</sub> channel, and the difference of the device performance

Figure 1. Multiple  $MoS_2$  FETs with MS and MIS contacts on a single monolayer  $MoS_2$  triangular domain. a) Schematic illustration of the fabrication process. b) False-colored SEM image of the MS-MS, MS-MIS (MIS-MS), and MIS-MIS FETs on a single  $MoS_2$  triangular domain as well as the corresponding cross-section schematics of the device structure. c) Raman spectrum of the monolayer  $MoS_2$  and h-BN. d) AFM image (inset) and scan profile of the monolayer  $MoS_2$ .

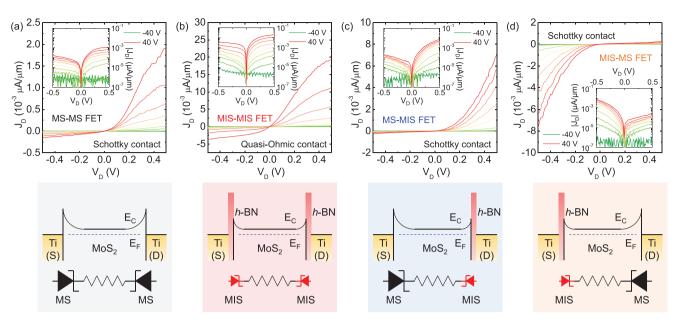

Figure 2. Comparison of output characteristics of  $MOS_2$  FETs with MS and MIS contacts. a–d) Top panel: Room-temperature  $J_D$ – $V_D$  characteristics in linear scale as well as logarithmic scale (inset) for the MS–MS, MIS–MIS, MS–MIS, and MIS–MS  $MOS_2$  FETs, respectively.  $V_G$  varies from –40 V (green) to 40 V (red) with a step of 10 V. Bottom panel: The corresponding energy band structures along the channel and the equivalent electronic circuits for all the types of the FETs with the MS and MIS contacts. For the ease of illustration and comparison, the effect of the applied  $V_D$  is not included. Here,  $E_C$  and  $E_F$  denote the conduction band edge and the Fermi energy level, respectively.

can be solely attributed to their contact conditions. We also fabricate the devices for transmission line measurement (TLM) to extract  $R_c$  with the MS and MIS contacts.

For all four transistor configurations, a comparison of drain current density (ID) versus drain voltage (VD) at various gate voltages  $(V_G)$  is performed in both linear and logarithmic scales at room temperature, as shown in Figure 2. There are several features to note. First, the  $J_{\rm D}{-}V_{\rm D}$  characteristics are not symmetric for the positive and negative  $V_D$  even with the same type of the contacts at the source and drain, due to an asymmetric contact condition (i.e., the different contact areas and thus the different  $R_c$  at the source and drain). Since each device is fabricated on a triangular corner, the device has a trapezoidal channel. We define the shorter metal contact as the source and the longer one as the drain for both the MS-MS and MIS-MIS FETs. The asymmetric factor, defined as the ratio of the current density magnitude at the positive  $V_D$  to that at the negative  $V_D$ , can be calculated as a function of  $V_{\rm D}$  for the MS-MS and MIS-MIS FETs, as shown in Figure S2 in the Supporting Information. Second, the MS-MS FET at  $V_G = 40 \text{ V}$  shows the highest  $J_{\rm D}$  of 1.2 nA  $\mu {\rm m}^{-1}$ , and it increases up to 19.3 nA  $\mu {\rm m}^{-1}$  for the MIS-MIS FET. For both the MS-MIS and MIS-MS FETs, the highest magnitude of  $I_D$  has an intermediate value of about 7 nA μm<sup>-1</sup>. The results clearly indicate that the introduction of the MIS contact, either at the source or drain end, can enhance the carrier transport and increase the current density. Third, a Schottky contact is observed in all the FETs which have at least one MS contact (i.e., the MS-MS, MS-MIS, and MIS-MS FETs), yet a quasi-Ohmic contact is obtained in the MIS-MIS FET. The superior performance of the MIS contact, including both the increased current density and the Schottky-to-Ohmic contact transition, can be interpreted by the quantum tunneling and barrier lowering which are induced by the decoration of the monolayer h-BN at the MS interface. Specifically, the conventional MS contact between Ti and  $MoS_2$  forms the Schottky barrier with an interacted interface, and the surface potential, defined as the difference between the metal and semiconductor work function, completely locates at the semiconductor side. Whereas the MIS contact has a monolayer h-BN and a van der Waals (vdW) gap ( $\approx$ 0.3 nm)<sup>[55]</sup> between Ti and  $MoS_2$ . These additional barriers with a total thickness of  $\approx$ 1 nm are still thin enough to allow the quantum tunneling occur with a high tunneling probability, but are thick enough to share the original surface potential, so the band bending on the  $MoS_2$  side and thus the effective SBH are reduced, giving rise to a smaller  $R_c$ .

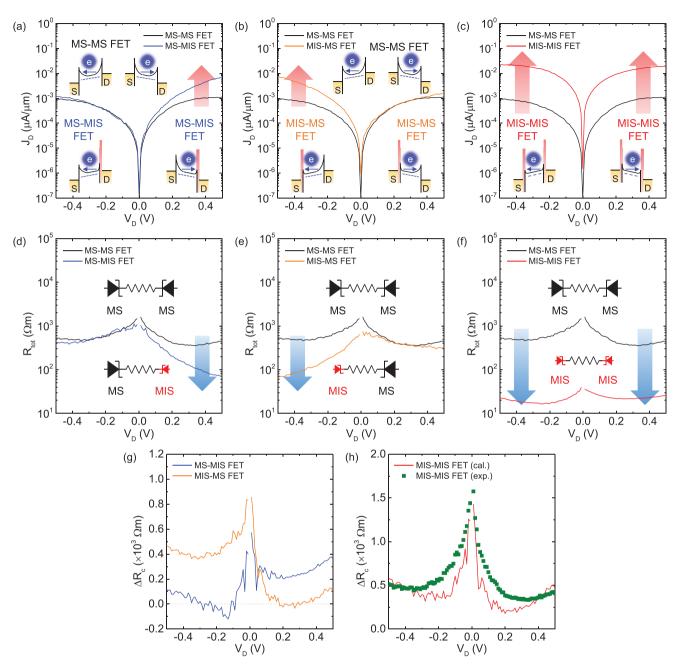

To further investigate the underlying mechanism of the MIS contact, here, we include the asymmetric factor at  $V_G = 40 \text{ V}$ and reconstruct the output characteristics at the same condition, as shown in Figure 3a-c. Here, the  $V_D$ -dependent asymmetric factor is an average based on the values obtained from both the MS-MS and MIS-MIS FETs (see Figure S2 in the Supporting Information), and is applied to eliminate the asymmetry between the source and drain contacts. Compared to the MS-MS FET, it is intriguing to see that the MIS contact, either at the drain in the MS-MIS FET or at the source in the MIS-MS FET, shows a novel and strong selectivity for the carrier transport through it. The electron transport from the semiconductor to the metal is significantly enhanced by a factor of  $\approx$ 7 (e.g., at  $V_{\rm D}$  = 0.5 V for the MIS drain contact in Figure 3a and at  $V_D = -0.5$  V for the MIS source contact in Figure 3b), but the transport from the metal to the semiconductor is negligibly affected (e.g., at  $V_D = -0.5$  V for the MIS drain contact in Figure 3a and at  $V_D = 0.5$  V for the MIS source contact in Figure 3b). Whereas, the MIS-MIS FET does not possess this selectivity anymore, due to a back-to-back connection of two MIS contacts, which are equivalently identical for the carrier

Figure 3. Diode-like selective enhancement of carrier transport through MIS contact. a–c) Comparison of the revised  $J_D$ – $V_D$  characteristics ( $V_G$  = 40 V) by including the asymmetric factor for the MS–MS, MS–MIS, MIS–MS, and MIS–MIS FETs, respectively. The MS–MS FET is used as a control sample. d–f) Comparison of the corresponding  $R_{tot}$  for the MS–MS, MS–MIS, MIS–MS, and MIS–MIS FETs, respectively. g,h) The calculated  $\Delta R_c$  as a function of  $V_D$  for the MS–MIS, MIS–MS, and MIS–MIS FETs, in a comparison with the experimental value obtained from the MIS–MIS FET.

transport from either direction (see Figure 3c). The maximum  $J_{\rm D}$  obtained at  $V_{\rm G}=40$  V in this FET is enhanced by a factor of  $\approx 20$ , which is higher than those in any other device.

Considering the description of  $J_{\rm D}{-}V_{\rm D}$  characteristics at a specific  $V_{\rm G}$  condition as  $J_{\rm D}=V_{\rm D}/R_{\rm tot}=V_{\rm D}/(R_{\rm cS}+R_{\rm cD}+R_{\rm ch})$ , it is possible to visualize the impact of the MIS contact on the  $V_{\rm D}$ -dependent resistances, as shown in Figure 3d–f. Here,  $R_{\rm tot}$ ,  $R_{\rm cS}$  (or  $R_{\rm cD}$ ), and  $R_{\rm ch}$  are the total resistance, the contact resistance at the source (or at the drain), and the channel resistance, respectively. It is clear to see that the value of  $R_{\rm tot}$  is significantly

reduced by introducing the MIS drain contact at the positive  $V_{\rm D}$  or the MIS source contact at the negative  $V_{\rm D}$ . Because both the MS  $R_{\rm c}$  and  $R_{\rm ch}$  are consistent for all the devices in comparison, the reduction of  $R_{\rm tot}$  directly indicates a decrease of  $R_{\rm c}$  ( $\Delta R_{\rm c}$ ) by exploiting the MIS contact, as shown in Figure 3g. The value of  $\Delta R_{\rm c}$  can reach up to  $\approx$ 400  $\Omega$  m (for the MIS drain contact at  $V_{\rm D}=0.5$  V and for the MIS source contact at  $V_{\rm D}=-0.5$  V) only when the electrons transport from the semiconductor to the metal, but approximates zero for the electron transport oppositely. Furthermore, by taking the sum of  $\Delta R_{\rm c}$  from the

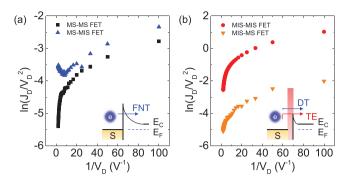

**Figure 4.** Impact of MS and MIS drain contacts on the carrier injection at the source. a,b) Comparison of  $\ln(J_D/V_D^2)$  versus  $1/V_D$  curves at  $V_G = 40$  V for the MS-source FETs (including the MS-MS and MS-MIS FETs) and the MIS-source FETs (including the MIS-MIS and MIS-MS FETs), respectively. Inset: Energy band diagram illustrates the FNT dominating in the MS-MIS FET, in a comparison with the DT and TE dominating in the MS-MS, MIS-MIS, and MIS-MS FETs.

MIS–MS and MS–MIS FETs, the overall reduction of  $R_{\rm c}$  for the MIS–MIS FET can be estimated as a function of  $V_{\rm D}$ , as shown in Figure 3h. The calculated  $\Delta R_{\rm c}$  in this method is in a good agreement with the experimental results, which is extracted from the difference of  $R_{\rm tot}$  between the MS–MS and MIS–MIS FETs. Its symmetric behavior for both the positive and negative  $V_{\rm D}$  is also consistent with the experimental data, serving as good evidence for the proposed theory.

We further investigate the dependence of the carrier transport on  $V_D$  by plotting  $\ln(J_D/V_D^2)$  versus  $1/V_D$  curves, as shown in Figure 4. For the MS-MS FET, no linear dependence is found even  $V_D$  is up to 2 V. However, by introducing the MIS drain contact in the MS-MIS FET, J-V linearity induced by Fowler-Nordheim tunneling (FNT) appears when  $V_D > 0.12$  V (see Figure 4a). Considering the identical MS source contact and the channel condition, it is clear that the drain contact plays an extremely important role in the overall transistor performance. The electron transport along the channel is governed by both the injection barrier at the source and the collection barrier at the drain, and thus the applied  $V_D$  is divided by  $R_{cS}$ ,  $R_{ch}$ , and  $R_{cD}$ . Due to the significant reduction of  $R_{cD}$  by introducing the MIS drain contact, the effective  $V_D$  drop over  $R_{cS}$  at the MS source contact becomes much higher compared to that in the MS-MS FET, and thus easily reaches to the threshold to enable the FNT at the MS source contact. In contrast, for the case of the MIS–MIS FET, a more effective  $V_{\rm D}$  drop is allocated over  $R_{\rm ch}$  due to the reduction of both  $R_{\rm cS}$  and  $R_{\rm cD}$ . Therefore, the carrier injection at the source is still dominated by direct tunneling (DT) and thermionic emission (TE) (see Figure 4b). The FNT at the source cannot occur unless a higher  $V_{\rm D}$  is applied.

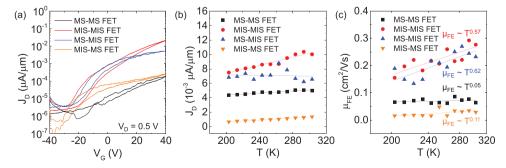

The  $J_D$ – $V_G$  transfer characteristics of all the types of the FETs are shown in **Figure 5**a. The MIS–MIS FET shows the best performance in terms of on-current density, on–off ratio, and subthreshold swing, whereas the MS–MS FET has the worst performance. The MS–MIS and MIS–MS FETs show the intermediate performance, and their difference is attributed to the asymmetric channel geometry and the assignment of the source and drain contacts. Similar results, together with the Schottky-to-Ohmic contact improvement, have also been reproduced from other devices using a thinner insulator for the back gating, as shown in Figure S3 in the Supporting Information.

For all the types of the FETs, their maximum  $J_D$  at  $V_D = 0.5$  V is obtained at  $V_G = 40$  V, and their temperature (*T*) dependence is measured from 203 to 303 K, as shown in Figure 5b and Figure S4 in the Supporting Information. As *T* increases, all the devices show an increase of  $I_D$  except for the MS-MIS FET. The virtual independence of the temperature suggests the quantum mechanical tunneling as the predominant carrier transport mechanism in the MS-MIS FET, which is also consistent with the demonstration of the FNT in our prior discussion (see Figure 4a). As a comparison, the MIS-MS FET shows a similar behavior like the MS-MS FET, because the MIS source contact under the positive  $V_D$  barely affects the electron transport from the metal to the semiconductor (see Figure 3b-e). The fieldeffect mobility ( $\mu_{FE}$ ), defined as  $(L/W)(1/C_{ox})(1/V_D)(\partial I_D/\partial V_G)$ , is calculated from the transfer characteristics, and the maximum values as a function of T are shown in Figure 5c. Here, L is the channel length, W is the average channel width, and  $C_{ox}$  is the capacitance of 285 nm thick SiO<sub>2</sub>. It has to be mentioned that the direct comparison of the  $\mu_{FE}$  values is not appropriate due to the asymmetry in the source and drain contacts as well as the channel geometry. However, their dependence on T, described by a power law as  $\mu_{\rm FE} \sim T^{\gamma}$ , can directly indicate the difference in the carrier transport mechanism. It is intriguing to see that all the devices with the MIS contact at the drain, either in the MIS-MIS or MS-MIS FETs, possess a strong and consistent temperature dependence of  $\mu_{\text{FE}}$ , and the exponent  $\gamma$  is obtained as ≈0.6. As a comparison, for all the devices with the MS contact at the drain, either in the MS-MS or MIS-MS FETs, the

**Figure 5.** Comparison of transfer characteristics of  $MoS_2$  FETs with MS and MIS contacts. a) Room-temperature  $J_D$ – $V_G$  characteristics in logarithmic scale for the MS–MS, MIS–MIS, MS–MIS, and MIS–MS  $MoS_2$  FETs at  $V_D = 0.5$  V. b) The maximum  $J_D$  obtained at  $V_G = 40$  V as a function of T for all the types of the FETs. c) The maximum  $\mu_{FF}$  as a function of T in logarithmic scale for all the types of the FETs.

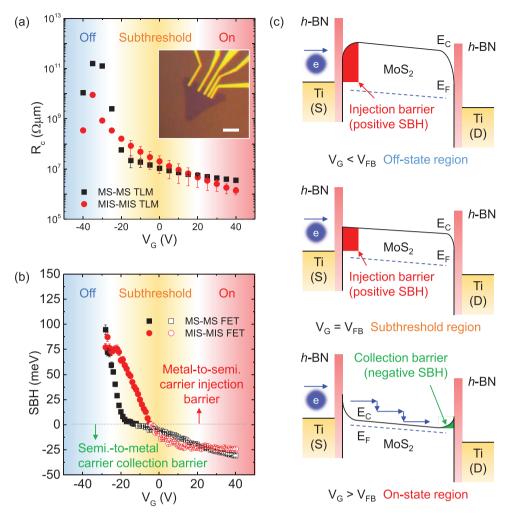

Figure 6. Comparison of contact resistance and barrier height with MS and MIS contacts. a) Room-temperature  $R_c$  as a function of  $V_G$  for the MS–MS and MIS–MIS TLM devices. The blue, yellow, and red backgrounds indicate the off-state, subthreshold, and on-state regions, respectively. Inset: Optical microscopy image of an MIS–MIS TLM device. Scale bar: 10  $\mu$ m. b) SBH as a function of  $V_G$  for the MS–MS and MIS–MIS FETs. The positive and negative SBHs indicate metal-to-semiconductor carrier injection barrier height (solid symbol) and semiconductor-to-metal carrier collection barrier height (hollow symbol), respectively. c) The corresponding energy band diagram along the channel for the MIS–MIS FET at a positive  $V_D$  and various  $V_G$  conditions ( $V_G < V_{FB}$ ,  $V_G = V_{FB}$ , and  $V_G > V_{FB}$ , where  $V_{FB}$  is the flat-band gate voltage). The predominant injection barrier at the off-state and subthreshold regions is highlighted in red, and the collection barrier at the on-state region is highlighted in green.

value of  $\mu_{\rm FE}$  has a relatively weak temperature dependence and  $\gamma$  approximates to  $\approx$ 0.1. This result clearly indicates that the drain contact for carrier collection plays an important role in the overall carrier transport and transistor performance. This result is also consistent with our prior discussion on the diodelike selective enhancement: the MIS contact can significantly affect the electron transport from the semiconductor to the metal (e.g., the MIS contact at the drain under the positive  $V_{\rm D}$ ) but barely vary the transport on the opposite direction (e.g., the MIS contact at the source under the positive  $V_{\rm D}$ ).

Following the discovery of the diode-like selective enhancement of the carrier transport through the MIS contact, we further investigate its impact on  $R_{\rm c}$  and SBH using the TLM and T-dependent measurements. Two TLM devices are fabricated with an identical structure, but one has the MS contacts and another one has the MIS contacts. The value of  $R_{\rm c}$  is extracted from a linear predication at room temperature and plotted as a function of  $V_{\rm G}$ , as shown in **Figure 6**a, where

the off-state, on-state, and subthreshold regions are identified based on the transfer characteristics in Figure 5a. In both the off-state and on-state regions,  $R_{\rm c}$  with the MS contact is higher compared to that with the MIS contact, but becomes lower in the subthreshold region.

The values of the SBH are extracted from the *T*-dependent output and transfer characteristics<sup>[18,56,57]</sup> in the MS–MS and MIS–MIS FETs, and they illustrate several important features, as shown in Figure 6b and Figure S5 in the Supporting Information. First, for both the MS–MS and MIS–MIS FETs, the SBH varies from positive to negative as the devices switch from the off-state to the on-state. The negative SBH has also been reported in the *h*-BN-decorated<sup>[48]</sup> or graphene-decorated metal contacts<sup>[58]</sup> not only for 2D materials but also for the conventional semiconductors.<sup>[59]</sup> Various underlying mechanisms are proposed and they are still under debate, for example, the overshadow effect by high series resistance<sup>[59,60]</sup> and the electric-field-driven modulation effect of the work functions.<sup>[58,61,62]</sup>

www.advancedsciencenews.com

www.advmat.de

Based on our experimental data, here, we propose a new theory using the concept of the collection barrier at the drain for interpretation. In the conventional approach to extract the thermionic SBH, the positive SBH is used to describe the energy potential barrier, which prevents the electron transport from the metal to the semiconductor at the source, and the contact at the drain is assumed to be an ideal Ohmic contact. However, if the drain contact is not an ideal case, the barrier at the drain could also prevent the electron collection, and thus the negative SBH can appeal, which describes the barrier preventing the carrier collection from the semiconductor to the metal. Here, we take the MIS-MIS FET as an example, and the energy band diagram with an applied positive  $V_D^{[63]}$  is shown in Figure 6c. When the transistor is at the off-state, the electron transport is primarily limited by the injection barrier at the source, and the drain contact acts as an Ohmic contact. As  $V_C$  increases, the transistor moves into the subthreshold region. When the transistor is at the on-state, the electron transport is mainly limited by the collection barrier at the drain, and the source contact is virtually transparent due to a high tunneling probability. Even the injected electrons have a relatively higher energy, most of the energy would be dissipated by collisions during the transport along the channel, and eventually face the collection barrier at the drain with the relatively low energy. Second, the absolute SBH value of the MIS-MIS FET, either for the carrier injection (positive SBH) or carrier collection (negative SBH), is always lower in the off- and on-state regions than that in the MS-MS FET but higher in the subthreshold region (see Figure 6b). This result is very consistent with the  $V_G$ -dependent  $R_c$  obtained from the TLM devices (see Figure 6a), serving as good evidence to prove the concept of the collection barrier. Third, although the collection barrier increases with  $V_G$ ,  $J_D$  still increases. This is because the 2D carrier density in the channel increases significantly with  $V_C$ . Considering the actual collection barrier height obtained in this work is only ≈30 meV at the maximum, its effect on the current is completely masked by the enlarged 2D carrier density as  $V_G$  increases.

Moreover, based on the energy band diagrams of the collection barrier (see Figure 6c), one can expect that the carrier transport mechanism through the MIS drain contact is a combination TE and quantum tunneling. When the collection barrier dominates, the electrons with high kinetic energies transport from the semiconductor to the metal by the DT, and the ones with low energies transport by the TE and thermionic field emission (TFE). As T increases, the electron distribution in the conduction band is widened to a higher energy range, and thus more electrons can tunnel through the MIS drain contact. This result is also consistent with the experimental observation of the strong T dependence of  $\mu_{\rm FE}$  in MIS–MIS and MS–MIS FETs (see Figure 5c).

In conclusion, we designed and fabricated the innovative device architecture to serve a new platform to investigate the 2D MS and MIS contacts in both symmetric and asymmetric conditions. We confirmed the improvement of the contact condition and consequently the enhancement of the device performance of  $MoS_2$  FETs by exploiting the MIS contacts decorated with the monolayer h-BN. Moreover, we revealed the novel diode-like selective enhancement of the carrier transport through the MIS contact. The MIS contact can significantly

reduce the contact resistance and boost the electron transport from the semiconductor to the metal, but barely affect the electron transport oppositely. With the concept of the carrier collection barrier, we revealed the underlying physics of the selective enhancement of the carrier transport through the MIS contact. We also interpreted the negative SBH obtained from the *T*-dependent measurement using the carrier collection barrier, in a comparison with the positive SBH described by the carrier injection barrier. Our work has advanced the fundamental understanding of 2D MIS contacts, and demonstrated the critical role of the collection barrier in the carrier transport of 2D nanoelectronic devices.

# **Experimental Section**

Material Synthesis and Characterization: The monolayer MoS<sub>2</sub> was synthesized using a customized two-zone CVD system.<sup>[53]</sup> Specifically, ammonium heptamolybdate (AHM) was used as a water-soluble Mo precursor, and NaOH was used as a water-soluble promoter. Their mixed solution was spin-coated on a SiO<sub>2</sub>/Si growth substrate. The reaction between Mo and Na produced Na<sub>2</sub>MoO<sub>4</sub> compounds and then became MoS<sub>2</sub> after S vapor injection. The annealing time was optimized to control the size of the isolated monolayer triangular domains. After synthesis, the monolayer MoS<sub>2</sub> flakes were wet-transferred onto a SiO<sub>2</sub>/Si device substrate. The large-area CVD-grown monolayer h-BN was purchased from 6Carbon Technology.<sup>[54]</sup> The Raman spectroscopy was performed by Renishaw inVia Raman microscope. The AFM analysis was performed by Bruker Dimension Icon with ScanAsyst.

Device Fabrication and Measurement: Both the FET and TLM devices were fabricated using electron-beam lithography (EBL) and evaporation with a Ti/Au (10 nm/100 nm) metal layer. Specifically, three types of global-back-gate transistors, including an MS-MS FET, an MIS-MIS FET, and an MS-MIS (or MIS-MS) FET, were fabricated on a single monolayer MoS2 triangular domain with the identical channel length and width (see Figure 1 and Figure S1 in the Supporting Information). To ensure a consistent channel width for the comparison of all the types of the transistors, here, the average value of the source and drain contact lengths were taken as the channel width for the trapezoidal geometry of the channel. All devices were fabricated on n-type Si substrates (0.001–0.005  $\Omega$  cm), which have 285 and 90 nm SiO<sub>2</sub> layers. The electrical measurements were performed in a vacuum-chamber probe station (MSTECH M5VC) with a semiconductor parameter analyzer (Keysight B1500A), and the temperature varied from 203 to 303 K.

## **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

# Acknowledgements

This work was partially supported by the National Science Foundation (NSF) under Award ECCS-1944095, the New York State Energy Research and Development Authority (NYSERDA) under Award 138126, and the New York State Center of Excellence in Materials Informatics (CMI) under Award C160186. This work was also partially supported by faculty startup funding from the University at Buffalo. The authors acknowledge support from the Vice President for Research and Economic Development (VPRED) at the University at Buffalo. A.C. acknowledges support from the Presidential Fellowship Program at the University at Buffalo.

#### **Conflict of Interest**

The authors declare no conflict of interest.

#### **Author Contributions**

F.Y. and H.L. conceived and supervised the project. J.L., C.C., and F.Y. synthesized the  $MoS_2$  samples. H.N.J. and R.D. fabricated the 2D FET and TLM devices. H.N.J., M.L., and S.S. performed the electrical characterizations. S.W. performed the material characterizations. A.C., Y.G., R.W., and J.M.L. participated in the sample preparation and device characterization. X.L. and C.Y. participated in the data analysis.

## **Keywords**

hexagonal boron nitride, MoS<sub>2</sub>, negative Schottky barrier, transistors

Received: April 21, 2020 Revised: June 21, 2020 Published online: July 28, 2020

- [1] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, A. Kis, *Nat. Nanotechnol.* **2011**, *6*, 147.

- [2] D. Lembke, S. Bertolazzi, A. Kis, Acc. Chem. Res. 2015, 48, 100.

- [3] Y. Yoon, K. Ganapathi, S. Salahuddin, Nano Lett. 2011, 11, 3768.

- [4] L. Liu, Y. Lu, J. Guo, IEEE Trans. Electron Devices 2013, 60, 4133.

- [5] Q. H. Wang, K. Kalantar-Zadeh, A. Kis, J. N. Coleman, M. S. Strano, Nat. Nanotechnol. 2012, 7, 699.

- [6] S. Das, J. A. Robinson, M. Dubey, H. Terrones, M. Terrones, Annu. Rev. Mater. Res. 2015, 45, 1.

- [7] M. Chhowalla, D. Jena, H. Zhang, Nat. Rev. Mater. 2016, 1, 16052.

- [8] G. Fiori, F. Bonaccorso, G. Iannaccone, T. Palacios, D. Neumaier, A. Seabaugh, S. K. Banerjee, L. Colombo, *Nat. Nanotechnol.* 2014, 9, 768.

- [9] D. Jariwala, V. K. Sangwan, L. J. Lauhon, T. J. Marks, M. C. Hersam, ACS Nano 2014, 8, 1102.

- [10] G. R. Bhimanapati, Z. Lin, V. Meunier, Y. Jung, J. Cha, S. Das, D. Xiao, Y. Son, M. S. Strano, V. R. Cooper, L. Liang, S. G. Louie, E. Ringe, W. Zhou, S. S. Kim, R. R. Naik, B. G. Sumpter, H. Terrones, F. Xia, Y. Wang, J. Zhu, D. Akinwande, N. Alem, J. A. Schuller, R. E. Schaak, M. Terrones, J. A. Robinson, ACS Nano 2015, 9, 11509.

- [11] F. Schwierz, J. Pezoldt, R. Granzner, Nanoscale 2015, 7, 8261.

- [12] D. S. Schulman, A. J. Arnold, S. Das, Chem. Soc. Rev. 2018, 47, 3037.

- [13] Y. Zhao, K. Xu, F. Pan, C. Zhou, F. Zhou, Y. Chai, Adv. Funct. Mater. 2017, 27, 1603484.

- [14] A. Allain, J. Kang, K. Banerjee, A. Kis, Nat. Mater. 2015, 14, 1195.

- [15] D. Jena, K. Banerjee, G. H. Xing, Nat. Mater. 2014, 13, 1076.

- [16] A. D. Franklin, Science 2015, 349, aab2750.

- [17] M. S. Choi, D. Qu, D. Lee, X. Liu, K. Watanabe, T. Taniguchi, W. J. Yoo, ACS Nano 2014, 8, 9332.

- [18] H. Li, D. Lee, D. Qu, X. Liu, J. Ryu, A. Seabaugh, W. J. Yoo, Nat. Commun. 2015, 6, 6564.

- [19] H. Fang, M. Tosun, G. Seol, T. C. Chang, K. Takei, J. Guo, A. Javey, Nano Lett. 2013, 13, 1991.

- [20] D. Kiriya, M. Tosun, P. Zhao, J. S. Kang, A. Javey, J. Am. Chem. Soc. 2014, 136, 7853.

- [21] A. Kutana, E. S. Penev, B. I. Yakobson, Nanoscale 2014, 6, 5820.

- [22] H. P. Komsa, A. V. Krasheninnikov, J. Phys. Chem. Lett. 2012, 3, 3652.

- [23] J. Xi, T. Zhao, D. Wang, Z. Shuai, J. Phys. Chem. Lett. 2014, 5, 285.

- [24] J. Kang, D. Sarkar, W. Liu, D. Jena, K. Banerjee, in 2012 IEEE Int. Electron Devices Meeting (IEDM), IEEE, Piscataway, NJ, USA 2012, pp. 17.4.1–17.4.4, https://doi.org/10.1109/IEDM.2012.6479060.

- [25] R. Kappera, D. Voiry, S. E. Yalcin, B. Branch, G. Gupta, A. D. Mohite, M. Chhowalla, *Nat. Mater.* 2014, 13, 1128.

- [26] Y. C. Lin, D. O. Dumcenco, Y. S. Huang, K. Suenaga, Nat. Nanotechnol. 2014, 9, 391.

- [27] C. Gong, L. Colombo, R. M. Wallace, K. Cho, Nano Lett. 2014, 14, 1714

- [28] M. Farmanbar, G. Brocks, Phys. Rev. B 2016, 93, 085304.

- [29] Y. Du, L. Yang, H. Liu, P. D. Ye, APL Mater. 2014, 2, 092510.

- [30] Y. K. Hong, G. Yoo, J. Kwon, S. Hong, W. G. Song, N. Liu, I. Omkaram, B. Yoo, S. Ju, S. Kim, M. S. Oh, AIP Adv. 2016, 6, 055026.

- [31] S. Das, H. Y. Chen, A. V. Penumatcha, J. Appenzeller, *Nano Lett.* 2013, 13, 100.

- [32] S. Chuang, C. Battaglia, A. Azcatl, S. McDonnell, J. S. Kang, X. Yin, M. Tosun, R. Kapadia, H. Fang, R. M. Wallace, A. Javey, *Nano Lett.* 2014. 14, 1337.

- [33] T. Musso, P. V. Kumar, A. S. Foster, J. C. Grossman, ACS Nano 2014, 8, 11432

- [34] Y. Liu, P. Stradins, S. H. Wei, Sci. Adv. 2016, 2, e1600069.

- [35] M. H. D. Guimaraes, H. Gao, Y. Han, K. Kang, S. Xie, C. J. Kim, D. A. Muller, D. C. Ralph, J. Park, ACS Nano 2016, 10, 6392.

- [36] J. Zheng, X. Yan, Z. Lu, H. Qiu, G. Xu, X. Zhou, P. Wang, X. Pan, K. Liu, L. Jiao, Adv. Mater. 2017, 29, 1604540.

- [37] C. D. English, G. Shine, V. E. Dorgan, K. C. Saraswat, E. Pop, Nano Lett. 2016, 16, 3824.

- [38] Y. Du, L. Yang, J. Zhang, H. Liu, K. Majumdar, P. D. Kirsch, P. D. Ye,in 72nd Device Research Conf. (DRC), IEEE, Piscataway, NJ, USA 2014, p. 147, https://doi.org/10.1109/DRC.2014.6872340.

- [39] Y. Du, L. Yang, J. Zhang, H. Liu, K. Majumdar, P. D. Kirsch, P. D. Ye, IEEE Electron Device Lett. 2104, 35, 599.

- [40] W. S. Leong, X. Luo, Y. Li, K. H. Khoo, S. Y. Quek, J. T. L. Thong, ACS Nano 2015, 9, 869.

- [41] Y. Liu, H. Wu, H. C. Cheng, S. Yang, E. Zhu, Q. He, M. Ding, D. Li, J. Guo, N. O. Weiss, Y. Huang, X. Duan, *Nano Lett.* 2015, 15, 3030.

- [42] S. Lee, A. Tang, S. Aloni, H.-S. Philip Wong, Nano Lett. 2016, 16, 276.

- [43] W. Park, Y. Kim, S. K. Lee, U. Jung, J. H. Yang, C. Cho, Y. J. Kim, S. K. Lim, I. S. Hwang, H. R. Lee, B. H. Lee, in 2014 IEEE Int. Electron Devices Meeting (IEDM), IEEE, Piscataway, NJ, USA 2014, pp. 5.1.1–5.1.4, https://doi.org/10.1109/IEDM.2014.7046986.

- [44] N. Kaushik, D. Karmakar, A. Nipane, S. Karande, S. Lodha, ACS Appl. Mater. Interfaces 2016, 8, 256.

- [45] J. R. Chen, P. M. Odenthal, A. G. Swartz, G. C. Floyd, H. Wen, K. Y. Luo, R. K. Kawakami, *Nano Lett.* 2013, 13, 3106.

- [46] M. Farmanbar, G. Brocks, Phys. Rev. B 2015, 91, 161304.

- [47] J. Su, L. Feng, W. Zeng, Z. Liu, Phys. Chem. Chem. Phys. 2016, 18, 31092.

- [48] J. Wang, Q. Yao, C. W. Huang, X. Zou, L. Liao, S. Chen, Z. Fan, K. Zhang, W. Wu, X. Xiao, C. Jiang, W. W. Wu, Adv. Mater. 2016, 28, 8302.

- [49] X. Cui, E. M. Shih, L. A. Jauregui, S. H. Chae, Y. D. Kim, B. Li, D. Seo, K. Pistunova, J. Yin, J.-H. Park, H.-J. Choi, Y. H. Lee, K. Watanabe, T. Taniguchi, P. Kim, C. R. Dean, J. C. Hone, *Nano Lett.* 2017, 17, 4781.

- [50] T. S. Ghiasi, J. Quereda, B. J. V. Wees, 2D Mater. 2019, 6, 015002.

- [51] L. H. Li, J. Cervenka, K. Watanabe, T. Taniguchi, Y. Chen, ACS Nano 2014, 8, 1457.

- [52] L. H. Li, Y. Chen, Adv. Funct. Mater. 2016, 26, 2594.

- [53] H. Kim, G. H. Han, S. J. Yun, J. Zhao, D. H. Keum, H. Y. Jeong, T. H. Ly, Y. Jin, J. H. Park, B. H. Moon, S. W. Kim, Y. H. Lee, *Nanotechnology* 2017, 28, 36LT01.

www.advancedsciencenews.com

www.advmat.de

- [54] 6Carbon Technology, http://www.6carbon.com/about-en.php (accessed: July 2019).

- [55] L. F. Mattheiss, Phys. Rev. B 1973, 8, 3719.

- [56] H. Li, D. Y. Lee, M. S. Choi, D. Qu, X. Liu, C. H. Ra, W. J. Yoo, Sci. Rep. 2015, 4, 4041.

- [57] M. Liu, S. Wei, S. Shahi, H. N. Jaiswal, P. Paletti, S. Fathipour, M. Remskar, J. Jiao, W. Hwang, F. Yao, H. Li, *Nanoscale*, https://doi. org/10.1039/D0NR01573C.

- [58] D. Qiu, E. K. Kim, Sci. Rep. 2015, 5, 13743.

- [59] M. Tao, D. Udeshi, S. Agarwal, E. Maldonado, W. P. Kirk, Solid-State Electron. 2004, 48, 335.

- [60] J. Osvald, Solid-State Electron. 2004, 48, 2347.

- [61] Y. J. Yu, Y. Zhao, S. Ryu, L. E. Brus, K. S. Kim, P. Kim, Nano Lett. 2009, 9, 3430.

- [62] Y. Li, C. Y. Xu, B. Y. Zhang, L. Zhen, Appl. Phys. Lett. 2013, 103, 033122.

- [63] A. Di Bartolomeo, A. Grillo, F. Urban, L. Iemmo, F. Giubileo, G. Luongo, G. Amato, L. Croin, L. Sun, S.-J. Liang, L. K. Ang, Adv. Funct. Mater. 2018, 28, 1800657.