www.acsnano.org

# 1,000,000 On/Off Ratio in Sub-1 nm Channel Length Carbon Nanotube/Monolayer MoS<sub>2</sub>/ Carbon Nanotube Vertical Transistors

Van Dam Do, Ngoc Thanh Duong, Van Tu Vu, Minh Chien Nguyen, Vu Khac Dat, Hai Phuong Duong, Dinh Phuc Do, Thanh Luan Phan, Hong Woon Yun, Seong Chu Lim, Anthony Cabanillas, Huamin Li, and Woo Jong Yu\*

Cite This: ACS Nano 2025, 19, 22291–22300

**ACCESS** I

III Metrics & More

Article Recommendations

s Supporting Information

ABSTRACT: Vertical field effect transistors (VFETs) using graphene and transition metal dichalcogenide (TMD) heterostructures are promising for downsizing the channel length to a monolayer TMD thickness of 0.65 nm. However, graphene/monolayer TMD/metal VFETs struggle with a low on/off ratio due to gate field screening by the graphene layer and a high offstate tunneling current caused by the large contact area. Here, we propose a 0.65 nm channel length VFET with a very high on/off current ratio made by cross-stacking top and bottom carbon nanotubes (CNTs) with a monolayer TMD in between. The ultranarrow junction area in the CNT/monolayer TMD/CNT VFET can significantly reduce the off-state tunneling current. Additionally, the gate field is transmitted from the

sidewall of the bottom CNT to the monolayer MoS<sub>2</sub> vertical channel between the two CNTs without field screening, achieving very strong gate modulation. As a result, our devices exhibit about 10<sup>5</sup> times higher on/off ratio (a maximum of 10<sup>6</sup>), 10<sup>5</sup> times lower off current (10<sup>-13</sup> A), and 560 times lower subthreshold swing (SS) (125 mV dec<sup>-1</sup>) compared to graphene/monolayer TMD/metal VFETs. In the comparison between multilayer MoS<sub>2</sub> and monolayer MoS<sub>2</sub> VFETs, rigid multilayer MoS<sub>2</sub> forms a large air gap at the multilayer MoS<sub>2</sub>/CNT/substrate, which reduces electric field transmission. In contrast, monolayer MoS<sub>2</sub> bends significantly along the sidewall of the CNT, resulting in minimal air gap formation and enhancing the electric field effect in the channel. As a result, the CNT/monolayer MoS<sub>2</sub>/CNT VFET shows a 10 times higher on-current saturation and on/off ratio compared to the CNT/multilayer MoS<sub>2</sub>/CNT VFET.

KEYWORDS: transition metal dichalcogenides, carbon nanotube, sub-1 nm channel length, vertical field effect transistor, chemical vapor deposition

# **INTRODUCTION**

enhance the direct tunneling current between the source and drain, leading to reduced on/off ratios and potential device failures due to short circuits.

To address these challenges, VFETs with van der Waals (vdW) heterostructures with sub-5 nm channel lengths have been proposed. This approach aims to improve interface contacts and prevent layer damage during fabrication, with the

Received: March 19, 2025 Revised: May 22, 2025 Accepted: May 22, 2025 Published: June 11, 2025

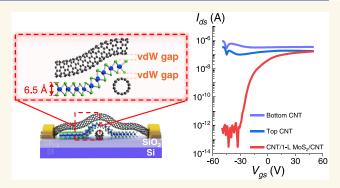

Figure 1. Structural characterization of the C/M/C VFET compared to graphene vdW contacts for the VFETs. (a) 3D schematic of the CNT/monolayer MoS<sub>2</sub>/CNT VFET. (b) Cross-sectional schematic of the C/M/C VFET with a monolayer MoS<sub>2</sub> sandwiched between two cross-stacked CNTs. (c) Optical microscope image of the C/M/C VFET. (d) False-colored SEM image of the C/M/C VFET with a monolayer MoS<sub>2</sub> as the channel. Inset: The green color represents a monolayer MoS<sub>2</sub> flake. (e) AFM topography image of the CNT<sub>B</sub>/MoS<sub>2</sub>/CNT<sub>T</sub> heterostructure. Inset: Height profiles of MoS<sub>2</sub>, CNT<sub>B</sub>, and CNT<sub>T</sub>. (f) Transfer characteristics of the C/M/C VFET compared to the graphene/MoS<sub>2</sub>/Ag VFET (reproduced with permission from ref 13. Copyright 2021 Springer Nature) at  $V_{\rm ds} = 0.1$  V. (g, h) Electrostatic simulations for the graphene/MoS<sub>2</sub>/Ag VFET at  $V_{\rm g} = 3$  V (on state, (g)) and  $V_{\rm g} = -3$  V (off state, (h)) with  $V_{\rm ds} = 0.1$  V. (i–j) Electrostatic simulations for the C/M/C VFET at  $V_{\rm g} = 3$  V (on state, (i)) and  $V_{\rm g} = -3$  V (off state, (j)) with  $V_{\rm ds} = 0.1$  V. The magenta arrows shown in (g–j) represent the magnitude and direction of the electric field.

semiconductor channel sandwiched between graphene and transferred metal electrodes. <sup>5,9,13,17</sup> However, the presence of the bottom graphene layer significantly screens the gate electric field, resulting in decreased electrostatic modulation of the gate on the TMD monolayer channel and a low on/off ratio of 26 in VFETs. <sup>13,18</sup>

Semimetal carbon nanotubes (CNTs) are emerging as promising candidates for tubular nanoscale wires, particularly when combined with two-dimensional (2D) materials to achieve multifunctionality and miniaturization due to their perfect tubular structure, <sup>19</sup> electrical and thermal stability, <sup>20,21</sup> and high current density. <sup>22</sup> Recently, CNTs have been utilized as electrodes in mixed-dimensional structures with a special emphasis on van der Waals integration. Examples include CNT/self-assembled molecule/CNT ferroelectric memory

(1D-0D-1D),<sup>23</sup> CNT with a 1 nm gate length for MoS<sub>2</sub> transistors (1D-2D),<sup>24</sup> single CNT/MoS<sub>2</sub>/Au vertical transistors (1D-2D-3D),<sup>12</sup> CNT network/MoS<sub>2</sub>/Au vertical transistors (1D-2D-3D),<sup>18</sup> CNT/MoS<sub>2</sub>/CNT planar transistors,<sup>25</sup> CNT/19 nm MoS<sub>2</sub>/CNT vertical transistors (1D-2D-1D),<sup>8</sup> and CNT/16 nm WSe<sub>2</sub>/14 nm MoS<sub>2</sub>/CNT p—n heterojunction photodetectors.<sup>26</sup> By stacking semimetal/semiconductor van der Waals contacts, it is possible to suppress metal-induced gap states (MIGS) and avoid Fermi-level pinning.<sup>27,28</sup> Moreover, the density of states (DOS) of CNTs is close to the Dirac point and low between the first van Hove singularities.<sup>29</sup> This characteristic allows for efficient gate-controlled modulation of the Fermi level through an external gate potential. Thus, individual CNTs present an excellent

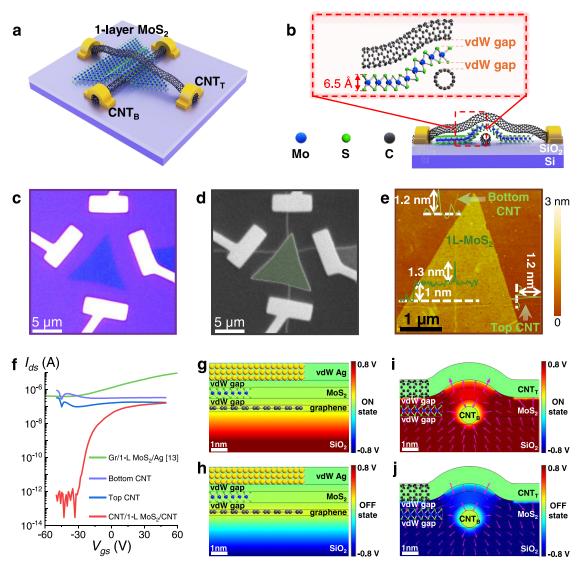

Figure 2. Electrical transport measurements are dependent on temperature. (a–c) Transfer characteristics of the 1L-MoS $_2$  C/M/C VFET (a), 2L-MoS $_2$  C/M/C VFET (b), and CNT planar FET (c) at  $V_{\rm ds}=0.1$  V under different temperatures. (d, e) Arrhenius plots of two individual CNTs sandwiching a monolayer MoS $_2$  (d) and a bilayer MoS $_2$  (e). (f) Gate-dependent BH of the 1L-MoS $_2$  and 2L-MoS $_2$  C/M/C VFET compared to the graphene/30 nm MoS $_2$ /Ti VFET (Reproduced with permission from ref 5. Copyright 2013 Springer Nature), graphene/5-layer MoS $_2$ /vdW Ag VFET (reproduced with permission from ref 13. Copyright 2021 Springer Nature), and CNT/19 nm MoS $_2$ /CNT VFET (reproduced with permission from ref 8. Copyright 2017 John Wiley & Sons, Inc.). (g, h) Energy band diagram of graphene/1-layer MoS $_2$ /metal (g) and CNT/1-layer MoS $_2$ /CNT (h) heterostructures.  $\Delta E_{\rm F}$  and  $\Delta \Phi$  represent the difference in Fermi levels and barrier heights under negative and positive gate voltages. (i) Electrostatic simulations for CNT/1L-MoS $_2$ /CNT VFETs with (top panel) and without vdW gaps (bottom panel) at  $V_{\rm g}=3$  V and  $V_{\rm ds}=0.1$  V.

alternative to graphene and metal electrodes for achieving the ultimate contact scaling in 2D nanodevices.

In this work, we propose a CNT/monolayer TMD/CNT (C/M/C) vdW vertical heterostructure to minimize the limitations of VFETs and prevent the tunneling current-induced short-circuit. The structure of the C/M/C VFET is demonstrated with monolayer MoS<sub>2</sub>, WSe<sub>2</sub>, and MoSe<sub>2</sub> sandwiched between cross-stacked CNTs. The screening effect in the C/M/C structure is significantly reduced by transmitting the gate field from the sidewall of the bottom CNT to the vertical channel of monolayer MoS<sub>2</sub>, allowing for direct modulation of the MoS<sub>2</sub> energy band. The ultranarrow junction area in the C/M/C VFET also reduces the off-state tunneling current. The CNT/MoS<sub>2</sub>/CNT junction demon-

strates a large barrier height (BH) change of 370 meV, which is significantly greater than the  $E_{\rm F}$  shift (20 meV with  $V_{\rm g}=-30-20$  V) of semimetallic CNTs. In contrast, the graphene/MoS<sub>2</sub> junction shows a smaller BH change (<92 meV) depending on the  $E_{\rm F}$  shift of graphene. Consequently, our C/M/C VFETs exhibit on/off ratios for VFETs with monolayer MoS<sub>2</sub> ( $10^5-10^6$ ), bilayer MoS<sub>2</sub> ( $10^5-10^6$ ), monolayer WSe<sub>2</sub> ( $10^4$ ), and monolayer MoSe<sub>2</sub> ( $10^3$ ) at room temperature. The subthreshold swing (SS) further improved with a decrease in the gate dielectric thickness from 300 nm SiO<sub>2</sub> (5 V dec<sup>-1</sup>) to 5.5 nm h-BN (125 mV dec<sup>-1</sup>). The monolayer C/M/C VFETs demonstrate even better electrical performance than the multilayer C/M/C VFETs. The rigid structure of multilayer MoS<sub>2</sub> creates a substantial air gap at the multilayer MoS<sub>2</sub>/

CNT/substrate heterostructure, diminishing the transmission of the electric field. In contrast, monolayer  $MoS_2$  bends significantly along the sidewall of the CNT, resulting in minimal air gap formation and, thus, enhancing the electric field effect within the channel. As a result, the monolayer C/M/C VFET shows a higher on/off ratio of  $10^6$  and on-current saturation at  $10^{-7}$  A compared to the multilayer C/M/C VFET (on/off ratio of  $10^5$  and on-current saturation at  $10^{-8}$  A).

# **RESULTS AND DISCUSSION**

Semimetal CNT-Sandwiched vdW Vertical Heterostructures for VFETs. Figure 1a shows the VFET configuration of a CNT/monolayer-MoS $_2$ /CNT heterostructure (C/M/C) on the SiO $_2$ /Si substrate. An overview of the fabrication process is provided in Figure S1 (Supporting Information). Briefly, the bottom CNT (CNT $_B$ ) was initially grown by using the chemical vapor deposition (CVD) technique and transferred to a silicon wafer coated with 300 nm SiO $_2$ . Monolayer MoS $_2$  was synthesized by CVD and transferred onto CNT $_B$ . Next, the top CNT (CNT $_T$ ) was cross-stacked on the CNT $_B$ /MoS $_2$  heterostructure. The metal electrodes were patterned on CNT $_B$  and CNT $_T$  using electron-beam lithography and deposited with Cr/Au (5/50 nm) through electron-beam deposition.

Figure 1b exhibits the cross-sectional schematic of the C/M/ C VFET, featuring vdW gaps formed from the physical stacking of the heterostructure with a channel length of 0.65 nm. Figure 1c displays an optical microscopy image of the C/ M/C VFET, in which a grown monolayer MoS<sub>2</sub> flake is transferred onto CNT<sub>B</sub>, and CNT<sub>T</sub> is aligned perpendicularly to CNT<sub>B</sub>. The presence of CNT<sub>T</sub> and CNT<sub>B</sub> can be confirmed by a scanning electron microscopy (SEM) image of the C/M/ C VFET, as shown in Figure 1d. Figure 1e exhibits an atomic force microscopy (AFM) topography image and height profile distribution of the C/M/C, revealing a clean surface of the CNT, MoS<sub>2</sub>, and the heterojunction, confirming a monolayer MoS<sub>2</sub> and a CNT thickness of 1.2 nm used in the C/M/C VFET. The Raman spectra of the CNT and monolayer MoS<sub>2</sub> on a Si/SiO<sub>2</sub> substrate are shown in Figure S2 (Supporting Information).

Figures 1f and S3 present the transfer characteristics of the top CNT, bottom CNT, and C/M/C VFET. The top and bottom CNT electrodes exhibit metallic behavior with no gate modulation, indicating that the gate modulation of the C/M/C VFET occurs only in the vertical monolayer MoS<sub>2</sub> channel. The C/M/C VFET shows an ultrahigh on/off ratio of 106, significantly higher than the previous graphene/monolayer MoS<sub>2</sub>/metal VFET, which had an on/off ratio of 26.<sup>13</sup> However, the off-state tunneling current increases proportionally with increasing  $V_{\rm ds}$  and causes the degradation of the on/ off ratio (Figure S4, Supporting Information). We also measured the graphene/monolayer MoS<sub>2</sub>/graphene heterostructure VFET (Figure S5, Supporting Information), showing a very small on/off ratio of 1.2. Notably, the large contact area of graphene/MoS<sub>2</sub>/metal and graphene/MoS<sub>2</sub>/graphene VFETs increases the off-state tunneling current to  $10^{-7}$  A,  $^{5,13}$ while the ultranarrow contact area in our C/M/C VFETs can significantly reduce the off-state tunneling current to  $10^{-13}$  A. The simulated electrical characteristics are employed to confirm that the ultranarrow junction area can significantly reduce the off-state tunneling current (Figure S6, Supporting Information). The ideal G/1L-M/G VFET exhibits a significantly higher tunneling current ( $10^{-1}$  A  $\mu m^{-2}$ ) than

the real device  $(10^{-6}~{\rm A}~\mu{\rm m}^{-2})$  due to the absence of contamination and the van der Waals gap in the ideal case. By normalizing the tunneling current to the VFET device area, we can extract the tunneling current for a given VFET device area (blue dashed line in Figure S6b).

To investigate the high on/off ratio in the C/M/C VFET compared to the previous graphene/monolayer MoS<sub>2</sub>/metal structure, the electrostatic potential of each device was simulated using a finite-element method conducted with COMSOL Multiphysics software (Figure 1g-j). The model parameters are listed in Table S1 (Supporting Information). In the electrostatic potential of graphene/monolayer MoS<sub>2</sub>/metal of the previous structure (Figure 1g,h), the gate electric field is mostly blocked by the graphene layer, and only a partial gate field is transmitted to the monolayer MoS<sub>2</sub>. In the C/M/C VFET (Figure 1i,j), in contrast, the gate electric field is transmitted from the sidewall of CNT<sub>B</sub> to the monolayer MoS<sub>2</sub> between the two CNTs without any field screening. Therefore, very strong gate modulation is achieved in the vertical C/M/C configuration. Such strong gate modulation in the C/M/C VFET is consistently observed in eight C/M/C VFETs with a maximum on/off ratio of  $1.01 \times 10^6$  (Figure S7, Supporting Information).

Barrier Height Profile of C/M/C VFETs under Gate **Modulation.** To investigate the gate modulation of the C/M/ C VFET, we measured temperature-dependent electrical characteristics of the C/M/C VFET. For the monolayer MoS<sub>2</sub> C/M/C VFET (1L-MoS<sub>2</sub> VFET), as the temperature decreases, the thermal activation of carriers in MoS<sub>2</sub> is suppressed, decreasing the off current of the 1L-MoS<sub>2</sub> VFET (Figures 2a and S8-S9, Supporting Information). With the excellent gate modulation of the 1L-MoS2 VFET, hole carrier inversion is observed in the negative gate region.<sup>30</sup> When increasing the channel thickness to bilayer MoS2 for the 2L-MoS<sub>2</sub> VFET (Figures S10–S11, Supporting Information), the 2L-MoS<sub>2</sub> VFET reduces the probability of carrier tunneling through the larger barrier, resulting in a reduced variation in the off-current state of transfer characteristics at low temperatures (Figures 2b and S12-S13, Supporting Information). The electrical characteristics of CNTs used as electrodes show negligible change at low temperatures (Figures 2c and S14, Supporting Information).

From the temperature-dependent studies, we have determined the BH  $(\Phi_B)$  across the junctions of CNT-MoS<sub>2</sub>. According to the thermionic emission theory,  $\Phi_{\rm B}$  at the CNT/ MoS<sub>2</sub> interfaces (Figure 2d,e) can be determined by the slopes of  $\ln(I_{\rm ds}/{\rm T}^{3/2})$  against q/kT for  $V_{\rm g}$  from the Arrhenius plot,<sup>31</sup> where  $I_{

m ds}$  is the drain-to-source current, T is the temperature, qis the elementary charge, and k is the Boltzmann constant. Figure 2f shows the derived BH from Figure 2d,e. The BH modulations ( $\Delta\Phi_{\rm B}$ ) at the CNT/monolayer MoS<sub>2</sub> and CNT/ bilayer MoS<sub>2</sub> junctions exhibit 370 and 594 meV, which are higher than those observed in graphene/30 nm MoS<sub>2</sub> [ref 5]  $(\Delta \Phi_{\rm B} = 234 \text{ meV})$ , graphene/5-layer MoS<sub>2</sub> [ref 13]  $(\Delta \Phi_{\rm B} =$ 92 meV) junctions, and CNT/19 nm MoS<sub>2</sub>/CNT VFET [ref 8] ( $\Delta\Phi_{\rm B}$  = 286 meV) junctions with the on-state BH saturated at 77 meV near a 6 V gate bias. It is noted that the difference in off-state barrier heights between 1L-MoS<sub>2</sub> and 2L-MoS<sub>2</sub> VFETs arises because the off-state barrier of the 1L-MoS<sub>2</sub> VFET (354 meV) is not sufficiently high to block thermally excited electrons, whereas the higher barrier of the 2L-MoS<sub>2</sub> VFET (573 meV) effectively suppresses the thermally activated carrier transport. The BH modulation of monolayer MoS<sub>2</sub>

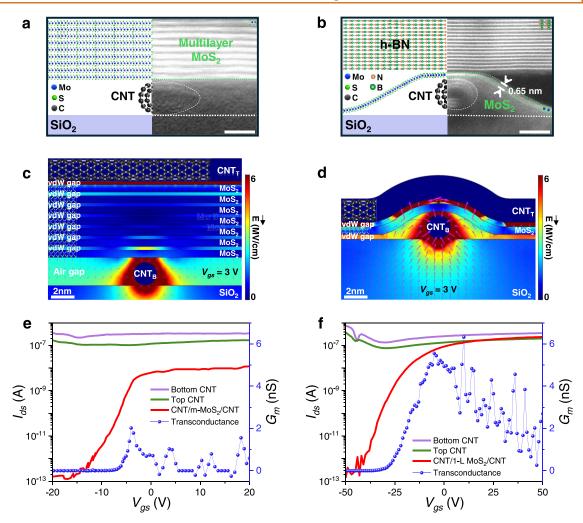

Figure 3. Comparison of multilayer and monolayer  $MoS_2$  stacked on CNTs for VFETs. (a, b) Cross-sectional STEM image of multilayer  $MoS_2$  (a) and monolayer  $MoS_2$  (b) stacked on individual CNTs forming a vdW gap of 0.35 nm. (c, d) Electric field (E) contour plots of  $CNT_B$ /multilayer  $MoS_2/CNT_T$  (c) and  $CNT_B$ /monolayer  $MoS_2/CNT_T$  (d) VFETs in the on state ( $V_g = 3$  V and  $V_{ds} = 0.1$  V). (e) Transfer curve (red line), transconductance (blue line) of the  $CNT_B$ /multilayer  $MoS_2/CNT_T$  VFET, and the transfer curve of bottom CNT (purple line) and top CNT FETs (green line) at  $V_{ds} = 0.1$  V (reproduced with permission from ref 8. Copyright 2017 John Wiley & Sons, Inc.). (f) Transfer curve (red line), transconductance (blue line) of the  $CNT_B$ /monolayer  $MoS_2/CNT_T$  VFET, and the transfer curve of bottom CNT (purple line) and top CNT FETs (green line) at  $V_{ds} = 0.1$  V.

VFETs should be lower than that of five-layer  $MoS_2$  due to the lower on/off ratio, although this has not been shown in previous studies. Furthermore, the CNT/ $MoS_2$  junction exhibits sharp BH modulation within  $V_{\rm g}$  = -20 - 0 V, whereas the graphene/ $MoS_2$  junction is modulated over a wide gate range of  $V_{\rm g}$  = -60 - 20 V.

The energy band diagrams of graphene/MoS<sub>2</sub>/metal and CNT/MoS<sub>2</sub>/CNT junctions are drawn based on the BH profiles (Figure 2g,h). In the graphene/MoS<sub>2</sub>/metal junction, the strong screening effect of graphene blocks the gate field, so the BH change of the graphene/MoS<sub>2</sub> junction is fully dependent on the Fermi level ( $E_{\rm F}$ ) shift of graphene by  $V_{\rm g}$  modulation, resulting in a small BH change. In contrast, the CNT/MoS<sub>2</sub>/CNT junction exhibits a very large BH change of 370 meV, which is larger than the typical  $E_{\rm F}$  shift (20 meV with  $V_{\rm g} = -30 - 20$  V) of semimetallic CNTs.<sup>32</sup> It is because the gate field is effectively transmitted from the sidewall of CNT<sub>B</sub> to the monolayer-MoS<sub>2</sub> vertical channel between the two CNTs without the field screening and directly modulates MoS<sub>2</sub>  $E_{\rm F}$ . It is noted that the vdW gap between MoS<sub>2</sub> and CNTs plays an important role in the large gate modulation.

Figure 2i shows the electrostatic potential simulation results with (top) and without the vdW gap (bottom panel). The gate modulation of the C/M/C VFET without the vdW gap shows a very small potential change at the  $CNT/MoS_2/CNT$  vertical junction due to the Fermi level pinning effect by metal-induced gap states (MIGS). On the other hand, the C/M/C VFET with the vdW gap can significantly reduce MIGS and Fermi level blocking effects.

Comparison between Multilayer and Monolayer MoS<sub>2</sub> in C/M/C VFETs. The difference in shape between multilayer MoS<sub>2</sub> and monolayer MoS<sub>2</sub> stacked on CNTs arises from their distinct structural and mechanical properties, which play a critical role in device performance. The cross-sectional scanning transmission electron microscopy (STEM) images provide clear evidence of the differences between the CNT–multilayer MoS<sub>2</sub> interface and the CNT–monolayer MoS<sub>2</sub> interface, as shown in Figure 3a,b, respectively. STEM/energy-dispersive spectroscopy (STEM-EDS) mapping of the CNT–multilayer MoS<sub>2</sub> and CNT–monolayer MoS<sub>2</sub> interfaces confirms the distribution of the main elements C, Mo, and S, as presented in Figures S15–S16 (Supporting Information),

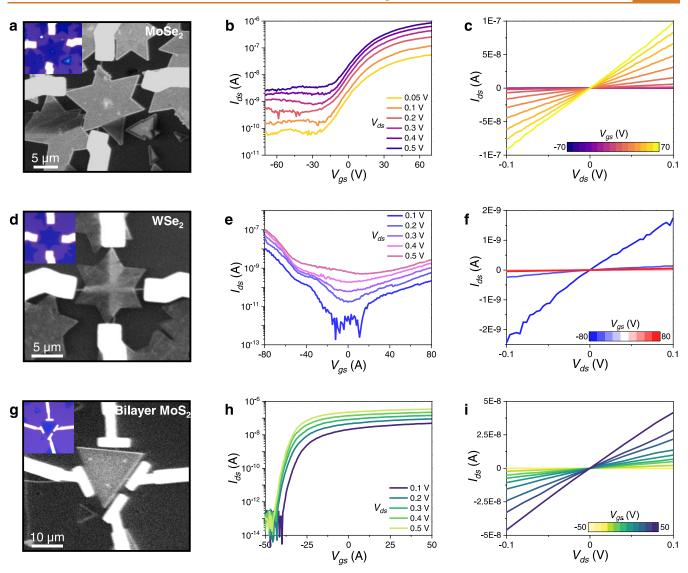

Figure 4. C/M/C VFETs based on monolayer MoSe<sub>2</sub>, monolayer WSe<sub>2</sub>, and bilayer MoS<sub>2</sub> channel lengths. (a, d, g) SEM images of monolayer MoSe<sub>2</sub> (a), monolayer WSe<sub>2</sub> C/M/C (d), and MoS<sub>2</sub> (g) C/M/C VFETs, with OM images of the devices shown in the inset. (b, e, h) Transfer curves of monolayer MoSe<sub>2</sub> (b), monolayer WSe<sub>2</sub> (e), and bilayer MoS<sub>2</sub> (h) C/M/C VFETs at room temperature. (c, f, i) Output curves of monolayer MoSe<sub>2</sub> (c), monolayer WSe<sub>2</sub> (f), and bilayer MoS<sub>2</sub> (i) C/M/C VFETs at room temperature.

respectively. When multilayer  $MoS_2$  is stacked on a CNT, it tends to exhibit flat layers because the vdW bonding of each layer in multilayer  $MoS_2$  leads to a rigid and stable structure without significant interlayer distortion. Such rigid multilayer  $MoS_2$  forms a large air gap between the multilayer  $MoS_2$  and the substrate when the CNT is sandwiched between them. In contrast, monolayer  $MoS_2$ , with its flexible and atomically thin structure, bends significantly when stacked on the CNT. This bending reduces the air gap between monolayer  $MoS_2$  and the substrate, which is expected to enhance the electric field effect in the channel.

To clarify the impact of the air gap on device performance, the electric field distribution is simulated for both the multilayer C/M/C VFET and monolayer C/M/C VFET at  $V_{\rm g}=3~{\rm V}$  and  $V_{\rm ds}=0.1~{\rm V}$  (at CNT\_B), as shown in Figure 3c,d, respectively. The electric field is significantly reduced in the air gap of the multilayer C/M/C VFET, while it retains its strength through the narrow vdW gap in the monolayer C/M/C VFET. Additionally, it is observed that the electric field in the multilayer C/M/C VFET gradually decreases across the

vdW gaps between the  $MoS_2$  layers. This reduction in the electric field within the multilayer C/M/C VFET weakens the gate modulation of the  $MoS_2$  channel. As a result, the multilayer C/M/C VFET exhibits an on/off ratio of  $10^5$  with limited on-current saturation of  $10^{-8}$  A (Figure 3e), while the monolayer C/M/C VFET shows a higher on/off ratio of  $10^6$  and on-current saturation at  $10^{-7}$  A (Figure 3f) limited by the current of CNT in comparison to the multilayer C/M/C VFET. Besides, the transconductance ( $G_{\rm m}$ ) of the monolayer C/M/C VFET is three times larger than that of the multilayer C/M/C VFET, indicating that the gate voltage can more effectively modulate the monolayer  $MoS_2$  channel.

Various Monolayer Semiconductor Materials in C/M/C VFETs. Benefiting from the C/M/C VFETs, chemical vapor deposition (CVD)-grown monolayer MoSe<sub>2</sub> and WSe<sub>2</sub> are employed to integrate with CNT electrodes for ultrashort-channel C/M/C VFETs. Figure 4a,d shows optical and SEM images of C/M/C VFETs for monolayer WSe<sub>2</sub> and MoSe<sub>2</sub> channel lengths, respectively. Raman, photoluminescence (PL), and atomic force microscopy (AFM) measurements

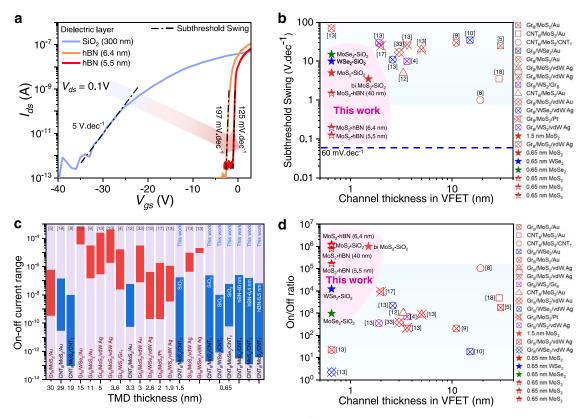

Figure 5. Performance comparison of C/M/C VFETs with other VFETs. (a) Transfer characteristics of C/M/C VFETs using MoS<sub>2</sub> channels with different h-BN dielectrics of 6.4 and 5.5 nm and a SiO<sub>2</sub> dielectric of 300 nm at  $V_{\rm ds} = 0.1$  V. The dashed lines represent the SS. (b) Benchmarking the SS along the channel length in VFETs (red: MoS<sub>2</sub>, blue: WSe<sub>2</sub>, purple: WS<sub>2</sub>, green: MoSe<sub>2</sub>). (c) Comparison of the on/off ratio of our C/M/C VFETs of monolayer MoSe<sub>2</sub>, MoSe<sub>2</sub>, and WSe<sub>2</sub> and bilayer MoS<sub>2</sub> with other VFETs. Note: VFETs use the bottom CNT (blue color) and the bottom graphene (red color) as the bottom electrode. (d) Benchmarking the on/off ratio along the channel length in VFETs (red: MoS<sub>2</sub>, blue: WSe<sub>2</sub>, purple: WS<sub>2</sub>, green: MoSe<sub>2</sub>). All reference values are shown in Table S2 (Supporting Information).

are utilized to confirm the structural characterization of WSe<sub>2</sub> and MoSe<sub>2</sub> C/M/C VFETs, as shown in Figures S17-S18 (Supporting Information). The transfer curves and output curves of MoSe<sub>2</sub> (Figure 4b,c) and WSe<sub>2</sub> C/M/C VFETs (Figure 4e,f) show high on/off ratios of 10<sup>3</sup> and 10<sup>4</sup> at room temperature, respectively. Other devices consistently exhibit the same performance, as shown in Figure S19 (Supporting Information). Additionally, the channel length increases from monolayer (0.65 nm) to bilayer (1.5 nm), as illustrated in OM and SEM images of the 2L-MoS<sub>2</sub> C/M/C VFET in Figure 4g. The transfer and output curves clearly show the improved suppression of the off-state current under high  $V_{ds}$  indicating effective mitigation of the drain-induced tunneling current (Figure 4h,i). Additional devices consistently exhibit high performance with on/off ratios of approximately 10°, as shown in Figure S20 (Supporting Information).

Performance Comparison of C/M/C VFETs with Other VFETs. To enhance the device performance, we used the thin h-BN layer as a gate insulator (Figures 5a and S21, Supporting Information). The transfer curve of the C/M/C VFET with a 300 nm SiO<sub>2</sub> gate insulator shows a subthreshold swing (SS) of 5 V dec<sup>-1</sup> and  $V_{\rm th}$  of -28 V. Using a 40 nm h-BN dielectric in the C/M/C VFET significantly reduces the SS to 1.5 V dec<sup>-1</sup> and  $V_{\rm th}$  to -9 V. Further decreasing the h-BN thickness to 6.4 and 5.5 nm results in an SS of 197 and 125 mV dec<sup>-1</sup> with  $V_{\rm th}$  of -2.5 and -0.9 V, respectively. Figure 5b and Table S2 (Supporting Information) show the SS comparison of C/M/C VFETs with other VFETs. 4,5,8=10,12,13,17,18,33 Our C/M/C VFETs with 5.5 nm h-BN achieve 560 times lower SS than

that of the previous monolayer  $MoS_2$  VFET (70 V  $dec^{-1}$ ). Furthermore, we demonstrate monolayer  $MoSe_2$  and  $WSe_2$  C/M/C VFETs for the first time, which exhibit similar SS on a  $SiO_2$  dielectric as multilayer  $WSe_2$ . Figure Sc,d and Table S2 (Supporting Information) compare the on/off ratio in VFETs with the reduction of channel length thickness.  $^{4,5,8-10,12,13,17,18,33}$  The graphene/ $MoS_2$ /metal and graphene/ $MoS_2$ /graphene VFETs generally exhibit a low on/off ratio due to gate field screening by the graphene layer, and the off-state tunneling current increases with decreasing TMD thickness. In contrast, C/M/C VFETs exhibit a high on/off ratio and low off-state tunneling current in overall TMD thicknesses because of the direct gate field modulation to the vertical channel and the ultranarrow vertical contact area.

# **CONCLUSIONS**

In summary, we have successfully demonstrated a CNT/monolayer TMD/CNT van der Waals vertical heterostructure as a promising solution to enhance the performance of VFETs. Our findings show that this configuration not only mitigates the inherent limitations faced by traditional VFETs but also provides significant advantages in terms of electrical performance. The ultranarrow junction area in the C/M/C structure effectively reduces off-state tunneling currents. Furthermore, the gate field is transmitted from the sidewall of the bottom CNT to the vertical TMD channel without screening. This leads to a remarkable on/off ratio of  $10^6$  for monolayer  $\rm MoS_2$  and even  $10^4$  for monolayer  $\rm WSe_2$  and  $\rm MoSe_2$  at room

temperature. Moreover, the implementation of thin h-BN as a gate insulator has further improved the subthreshold swing, demonstrating the potential for scaling down 2D transistors effectively. Our research lays a solid foundation for future investigations into the scaling and optimization of ultrathin VFETs, paving the way for next-generation electronic devices and maintaining the momentum of Moore's law.

## **METHODS**

**Synthesis of Aligned CNTs.** The aligned CNTs are synthesized by CVD using the C precursor from methane gas (99,99% purity). A mixed solution of alumina ( $Al_2O_3$ ) nanoparticles, bis(acetylacetonato)dioxo-molybdenum ( $MoO_2(acac)_2$ , 99.98%, Aldrich), poly-(vinylpyrrolidone) ( $M_w$  50,000, Aldrich), (Fe( $NO_3$ ) $_3$ -9 $H_2O$ , 99.99%, Aldrich), and IPA in deionized (DI) water is sonicated for 1 h. Next, one edge of a SiO $_2$ /Si substrate is dipped in the catalyst solution and dried at 110 °C. The substrate is put in the center of a quartz tube and the growth occurs at 1000 °C with a gas ratio of  $CH_4/H_2$  (10/20 sccm) for 40 min. After completion, argon gas is flowed, and the chamber is naturally cooled to room temperature.

Synthesis of Monolayer and Bilayer MoS<sub>2</sub>. Ammonium heptamolybdate (AHM, Sigma-Aldrich) as the Mo source was dissolved in DI water with an opti solution at a ratio of 0.5/0.5/3 (Mo/Opti/H<sub>2</sub>O). The catalyst solution was spin-coated on a SiO<sub>2</sub>/Si substrate and annealed at 500 °C to remove carbon from opti. Then, the substrate was located in the center of the quartz tube, and the sulfur (S) powder was in the upstream zone. For the growth of monolayer and bilayer MoS<sub>2</sub>, 600 mg and 1.5 g of S were melted at 200 °C at the S zone, while the reaction occurred at 800 °C with the flow of 100 sccm N<sub>2</sub> for 5 and 6 min, respectively. After completion, the chamber was cooled to room temperature.

**Synthesis of Monolayer WSe<sub>2</sub>.** Ammonium metatungstate (AMT) hydrate as the W precursor with NaOH powder and opti was dissolved in DI water at a ratio of 0.5/1/0.5 (W/NaOH/Opti). After the catalyst solution was spin-coated and annealed on the substrate, it was located in the middle of the tube, and the Se powder source was in an upstream region. For growth, the temperature was increased to 850 °C with a mixed gas of 300/30 sccm (N<sub>2</sub>/H<sub>2</sub>), and the reaction occurred in 5 min. After completion, the chamber was cooled to room temperature.

**Synthesis of Monolayer MoSe<sub>2</sub>.** Ammonium heptamolybdate (AHM, Sigma-Aldrich) was used as the Mo source. The preparation process was the same as that used for the growth of MoS<sub>2</sub>. However, Se powder was used to grow monolayer MoSe<sub>2</sub> flakes. For growth, the temperature was up to 850  $^{\circ}$ C with a gas ratio of 300/30 sccm (N<sub>2</sub>/H<sub>2</sub>), and the reaction took place for 4 min. After completion, the chamber was cooled to room temperature.

**Device Fabrication.** The aligned CNT<sub>B</sub> on the SiO<sub>2</sub>/Si substrate was coated with a PMMA solution and dried at 110  $^{\circ}\text{C}$  for 1 min. Then, the sample was floated on a 2% HF in a DI water mixture to separate the PMMA/CNT<sub>B</sub> film from the substrate due to the SiO<sub>2</sub> being etched. The PMMA/CNT<sub>B</sub> film was transferred to DI water to remove the HF solution and transferred onto a prime SiO<sub>2</sub>/Si substrate. The PMMA film was removed in acetone for 20 min. TMD flakes were transferred on the CNT<sub>B</sub>/SiO<sub>2</sub>/Si substrate by the wet transfer method, analogous to the procedure for CNT<sub>B</sub> transfer. The samples were annealed at 200 °C for 3 h under vacuum with 200 sccm of N<sub>2</sub> to eliminate the bubbles between the heterointerfaces. The aligned CNT<sub>T</sub> was dry-transferred on the TMD/CNT<sub>B</sub>/SiO<sub>2</sub>/Si substrate. The aligned CNT<sub>T</sub> was detached from the original substrate with the same method of transferring the aligned CNT<sub>B</sub>. The PET substrate was used to flip up the PMMA/CNT<sub>T</sub> film. Then, aligned CNT<sub>T</sub> was cross-aligned on top of the TMD/CNT<sub>B</sub> heterostructure. Lastly, the PMMA film was removed with acetone. The electrodes were patterned on CNTs by EBL and deposited for Cr/Au (5/50 nm) by an EBV system. The useless CNTs were etched by a reactiveion etching system with 30 sccm O2 gas.

**Measurements.** SEM images were taken on a JEOL, JSM-6510 instrument with an accelerating voltage of 1 kV. Raman and PL

spectra were obtained on an NTEGRA Spectra system at a 532 nm focused laser. The AFM was performed on a Park NX10, Park system. HR-STEM and EDS mapping were acquired on a JEM-ARM300CF, JEOL, Japan at 300 keV. Electrical measurements were measured on Keithley 4200 under low vacuum (2  $\times$  10 $^{-2}$  Torr) and on a closed-cycle refrigerator system at a low temperature under high vacuum (10 $^{-7}$  Torr).

## **ASSOCIATED CONTENT**

# Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsnano.5c04746.

Characterization of C/M/C heterostructures; electrical characterization of C/M/C VFETs; simulated electrical characteristics of C/M/C VFETs; temperature-dependent I-V characteristics; cross-sectional HRTEM micrographs of MoS $_2$ ; AFM of C/M/C VFETs, top-gate electrical characteristics, and table comparison (PDF)

## **AUTHOR INFORMATION**

# **Corresponding Author**

Woo Jong Yu — Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea; ⊚ orcid.org/0000-0002-7399-307X; Email: micco21@skku.edu

# **Authors**

Van Dam Do – Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea

Ngoc Thanh Duong – Department of Energy Science, Sungkyunkwan University, Suwon 16419, Republic of Korea

Van Tu Vu – Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea

Minh Chien Nguyen – Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea; orcid.org/0009-0001-6991-3591

**Vu Khac Dat** – Department of Energy Science, Sungkyunkwan University, Suwon 16419, Republic of Korea

Hai Phuong Duong – Department of Energy Science, Sungkyunkwan University, Suwon 16419, Republic of Korea

Dinh Phuc Do − Department of Chemistry, Sungkyunkwan University, Suwon 16419, Republic of Korea; orcid.org/0000-0001-5325-8660

Thanh Luan Phan — Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea; Occid.org/0000-0002-2873-8176

Hong Woon Yun – Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea

Seong Chu Lim — Department of Energy Science, Sungkyunkwan University, Suwon 16419, Republic of Korea; orcid.org/0000-0002-0751-1458

Anthony Cabanillas — Department of Electrical Engineering, University at Buffalo, The State University of New York, Buffalo, New York 14260, United States; orcid.org/0009-0002-0170-1899

Huamin Li – Department of Electrical Engineering, University at Buffalo, The State University of New York, Buffalo, New York 14260, United States; orcid.org/0000-0001-7093-4835

Complete contact information is available at: https://pubs.acs.org/10.1021/acsnano.5c04746

## **Author Contributions**

W.J.Y. and V.D.D. conceived the research. W.J.Y. and V.D.D. designed the experiment. V.D.D. performed the device fabrication, growth of CNTs and MoS<sub>2</sub>, COMSOL Multiphysics simulations, characterization, and data analysis. N.T.D. and S.C.L. contributed to the low-temperature measurement, V.T.V. and M.C.N. performed the growth of MoSe<sub>2</sub> and WSe<sub>2</sub>, V.K.D. and H.P.D. contributed to the device fabrication, D.P.D., A.C., and H.L. contributed to the data analysis, T.L.P. contributed to the growth of CNTs, and H.W.J. contributed to the simulation. The paper was written by V.D.D. and W.J.Y. with contributions from all the coauthors.

#### Notes

The preprint version of this manuscript is available at: V.D.D., N.T.D., V.T.V., M.C.N., V.K.D., H.P.D., D.P.D., T.L.P., H.W.Y., S.C.L, W.J.Y.. 1,000,000 on/off Ratio in Sub-1 nm Channel Length CNT/Monolayer MoS<sub>2</sub>/CNT Vertical Transistors, 2024, Research Square. 10.21203/rs.3.rs-5122148/v1. The authors declare no competing financial interest.

#### **ACKNOWLEDGMENTS**

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT) (NRF-2021R1A2C2004027, NRF-2023K2A9A2A06059788, NRF-2020R1A5A1019649, RS-2024-00439520, RS-2024-00439092, RS-2025-05682968), ICT Creative Consilience program (IITP-2020-0-01821), and the Competency Development Program for Industry Specialists of the Korean Ministry of Trade, Industry and Energy (MOTIE), operated by the Korea Institute for Advancement of Technology (KIAT) (No. P0023704, Semiconductor-Track Graduate School (SKKU)). Additional support was provided by the Samsung Research Funding & Incubation Center of Samsung Electronics under Project No. SRFC-MA1701-01.

# **REFERENCES**

- (1) Geim, A. K.; Grigorieva, I. V. Van Der Waals Heterostructures. *Nature* **2013**, 499, 419–425.

- (2) Liu, Y.; Weiss, N. O.; Duan, X.; Cheng, H. C.; Huang, Y.; Duan, X. Van Der Waals Heterostructures and Devices. *Nat. Rev. Mater.* **2016**, *1*, No. 16042.

- (3) Novoselov, K. S.; Mishchenko, A.; Carvalho, A.; Neto, A. H. C. 2D Materials and van Der Waals Heterostructures. *Science* **2016**, *353*, No. aac9439.

- (4) Georgiou, T.; Jalil, R.; Belle, B. D.; Britnell, L.; Gorbachev, R. V.; Morozov, S. V.; Kim, Y. J.; Gholinia, A.; Haigh, S. J.; Makarovsky, O.; Eaves, L.; Ponomarenko, L. A.; Geim, A. K.; Novoselov, K. S.; Mishchenko, A. Vertical Field-Effect Transistor Based on Graphene-WS 2 Heterostructures for Flexible and Transparent Electronics. *Nat. Nanotechnol.* **2013**, *8*, 100–103.

- (5) Yu, W. J.; Li, Z.; Zhou, H.; Chen, Y.; Wang, Y.; Huang, Y.; Duan, X. Vertically Stacked Multi-Heterostructures of Layered Materials for Logic Transistors and Complementary Inverters. *Nat. Mater.* **2013**, 12, 246–252.

- (6) Britnell, L.; Gorbachev, R. V.; Jalil, R.; Belle, B. D.; Schedin, F.; Mishchenko, A.; Georgiou, T.; Katsnelson, M. I.; Eaves, L.; Morozov, S. V.; Peres, N. M. R.; Leist, J.; Geim, A. K.; Novoselov, K. S.; Ponomarenko, L. A. Field-Effect Tunneling Transistor Based on Vertical Graphene Heterostructures. *Science* 2012, 335, 947–950.

- (7) Yu, W. J.; Liu, Y.; Zhou, H.; Yin, A.; Li, Z.; Huang, Y.; Duan, X. Highly Efficient Gate-Tunable Photocurrent Generation in Vertical

- Heterostructures of Layered Materials. Nat. Nanotechnol. 2013, 8, 952-958.

- (8) Zhang, J.; Wei, Y.; Yao, F.; Li, D.; Ma, H.; Lei, P.; Fang, H.; Xiao, X.; Lu, Z.; Yang, J.; Li, J.; Jiao, L.; Hu, W.; Liu, K.; Liu, K.; Liu, P.; Li, Q.; Lu, W.; Fan, S.; Jiang, K. SWCNT-MoS2-SWCNT Vertical Point Heterostructures. *Adv. Mater.* **2017**, *29*, No. 1604469.

- (9) Choi, Y.; Kang, J.; Jariwala, D.; Kang, M. S.; Marks, T. J.; Hersam, M. C.; Cho, J. H. Low-Voltage Complementary Electronics from Ion-Gel-Gated Vertical Van Der Waals Heterostructures. *Adv. Mater.* **2016**, 28, 3742–3748.

- (10) Shin, Y. S.; Lee, K.; Kim, Y. R.; Lee, H.; Lee, I. M.; Kang, W. T.; Lee, B. H.; Kim, K.; Heo, J.; Park, S.; Lee, Y. H.; Yu, W. J. Mobility Engineering in Vertical Field Effect Transistors Based on Van Der Waals Heterostructures. *Adv. Mater.* **2018**, *30*, No. 1704435.

- (11) Yu, W. J.; Vu, Q. A.; Oh, H.; Nam, H. G.; Zhou, H.; Cha, S.; Kim, J. Y.; Carvalho, A.; Jeong, M.; Choi, H.; Castro Neto, A. H.; Lee, Y. H.; Duan, X. Unusually Efficient Photocurrent Extraction in Monolayer van Der Waals Heterostructure by Tunnelling through Barriers. *Nat. Commun.* **2016**, *7*, No. 13278.

- (12) Zhang, J.; Zhang, K.; Xia, B.; Wei, Y.; Li, D.; Zhang, K.; Zhang, Z.; Wu, Y.; Liu, P.; Duan, X.; Xu, Y.; Duan, W.; Fan, S.; Jiang, K. Carbon-Nanotube-Confined Vertical Heterostructures with Asymmetric Contacts. *Adv. Mater.* **2017**, *29*, No. 1702942.

- (13) Liu, L.; Kong, L.; Li, Q.; He, C.; Ren, L.; Tao, Q.; Yang, X.; Lin, J.; Zhao, B.; Li, Z.; Chen, Y.; Li, W.; Song, W.; Lu, Z.; Li, G.; Li, S.; Duan, X.; Pan, A.; Liao, L.; Liu, Y. Transferred van Der Waals Metal Electrodes for Sub-1 nm MoS2 Vertical Transistors. *Nat. Electron.* **2021**, *4*, 342–347.

- (14) Chhowalla, M.; Jena, D.; Zhang, H. Two-Dimensional Semiconductors for Transistors. *Nat. Rev. Mater.* **2016**, *1*, No. 16052.

- (15) Migita, S.; Morita, Y.; Masahara, M.; Ota, H. In *Electrical Performances of Junctionless-FETs at the Scaling Limit (L CH = 3 nm)*, International Electron Devices Meeting; IEEE, 2012.

- (16) Liu, Y.; Guo, J.; Zhu, E.; Liao, L.; Lee, S.-J.; Ding, M.; Shakir, I.; Gambin, V.; Huang, Y.; Duan, X. Approaching the Schottky—Mott Limit in van Der Waals Metal—Semiconductor Junctions. *Nature* **2018**, *557*, 696—700.

- (17) Ma, L.; Tao, Q.; Chen, Y.; Lu, Z.; Liu, L.; Li, Z.; Lu, D.; Wang, Y.; Liao, L.; Liu, Y. Realizing On/Off Ratios over 104 for Sub-2 nm Vertical Transistors. *Nano Lett.* **2023**, 23, 8303–8309.

- (18) Phan, T. L.; Vu, Q. A.; Kim, Y. R.; Shin, Y. S.; Lee, I. M.; Tran, M. D.; Jiang, J.; Luong, D. H.; Liao, L.; Lee, Y. H.; Yu, W. J. Efficient Gate Modulation in a Screening-Engineered MoS2/Single-Walled Carbon Nanotube Network Heterojunction Vertical Field-Effect Transistor. ACS. Appl. Mater. Interfaces 2019, 11, 25516–25523.

- (19) Iijima, S.; Ichihashi, T. Single-Shell Carbon Nanotubes of 1-nm Diameter. *Nature* **1993**, *363*, *603*–*605*.

- (20) White, C. T.; Todorov, T. N. Carbon Nanotubes as Long Ballistic Conductors. *Nature* **1998**, 393, 240–242.

- (21) Liew, K. M.; Wong, C. H.; He, X. Q.; Tan, M. J. Thermal Stability of Single and Multi-Walled Carbon Nanotubes. *Phys. Rev. B* **2005**, *71*, No. 075424.

- (22) Yao, Z.; Kane, C. L.; Dekker, C. High-Field Electrical Transport in Single-Wall Carbon Nanotubes. *Phys. Rev. Lett.* **2000**, 84, No. 2941.

- (23) Phan, T. L.; Seo, S.; Cho, Y.; An Vu, Q.; Lee, Y. H.; Duong, D. L.; Lee, H.; Yu, W. J. CNT-Molecule-CNT (1D-0D-1D) van Der Waals Integration Ferroelectric Memory with 1-Nm2 Junction Area. *Nat. Commun.* 2022, *13*, No. 4556.

- (24) Desai, S. B.; Madhvapathy, S. R.; Sachid, A. B.; Llinas, J. P.; Wang, Q.; Ahn, G. H.; Pitner, G.; Kim, M. J.; Bokor, J.; Hu, C.; Wong, H. S. P.; Javey, A. MoS2 Transistors with 1-Nanometer Gate Lengths. *Science* **2016**, *354*, 99–102.

- (25) Li, X.; Wei, Y.; Wang, Z.; Kong, Y.; Su, Y.; Lu, G.; Mei, Z.; Su, Y.; Zhang, G.; Xiao, J.; Liang, L.; Li, J.; Li, Q.; Zhang, J.; Fan, S.; Zhang, Y. One-Dimensional Semimetal Contacts to Two-Dimensional Semiconductors. *Nat. Commun.* **2023**, *14*, No. 111.

- (26) Zhang, J.; Cong, L.; Zhang, K.; Jin, X.; Li, X.; Wei, Y.; Li, Q.; Jiang, K.; Luo, Y.; Fan, S. Mixed-Dimensional Vertical Point p -n Junctions. ACS Nano 2020, 14, 3181–3189.

- (27) Zhai, E.; Liang, T.; Liu, R.; Cai, M.; Li, R.; Shao, Q.; Su, C.; Lin, Y. C. The Rise of Semi-Metal Electronics. *Nat. Rev. Electr. Eng.* **2024**, *1*, 497–515.

- (28) Liu, X.; Choi, M. S.; Hwang, E.; Yoo, W. J.; Sun, J. Fermi Level Pinning Dependent 2D Semiconductor Devices: Challenges and Prospects. *Adv. Mater.* **2022**, *34*, No. 2108425.

- (29) Wilder, J. W. G.; Venema, L. C.; Rinzler, A. G.; Smalley, R. E.; Dekker, C. Electronic Structure of Atomically Resolved Carbon Nanotubes. *Nature* **1998**, *391*, 59–62.

- (30) Kim, S.; Konar, A.; Hwang, W. S.; Lee, J. H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J. B.; Choi, J. Y.; Jin, Y. W.; Lee, S. Y.; Jena, D.; Choi, W.; Kim, K. High-Mobility and Low-Power Thin-Film Transistors Based on Multilayer MoS2 Crystals. *Nat. Commun.* **2012**, 3, No. 1011.

- (31) Wang, Y.; Kim, J. C.; Wu, R. J.; Martinez, J.; Song, X.; Yang, J.; Zhao, F.; Mkhoyan, A.; Jeong, H. Y.; Chhowalla, M. Van Der Waals Contacts between Three-Dimensional Metals and Two-Dimensional Semiconductors. *Nature* **2019**, *568*, 70–74.

- (32) Li, X.; Wei, Y.; Lu, G.; Mei, Z.; Zhang, G.; Liang, L.; Li, Q.; Fan, S.; Zhang, Y. Gate-Tunable Contact-Induced Fermi-Level Shift in Semimetal. *Proc. Natl. Acad. Sci. U.S.A.* **2022**, *119*, No. e2119016119.

- (33) Xiao, Z.; Liu, L.; Chen, Y.; Lu, Z.; Yang, X.; Gong, Z.; Li, W.; Kong, L.; Ding, S.; Li, Z.; Lu, D.; Ma, L.; Liu, S.; Liu, X.; Liu, Y. High-Density Vertical Transistors with Pitch Size Down to 20 nm. *Adv. Sci.* **2023**, *10*, No. 2302760.

CAS BIOFINDER DISCOVERY PLATFORM™

# CAS BIOFINDER HELPS YOU FIND YOUR NEXT BREAKTHROUGH FASTER

Navigate pathways, targets, and diseases with precision

**Explore CAS BioFinder**